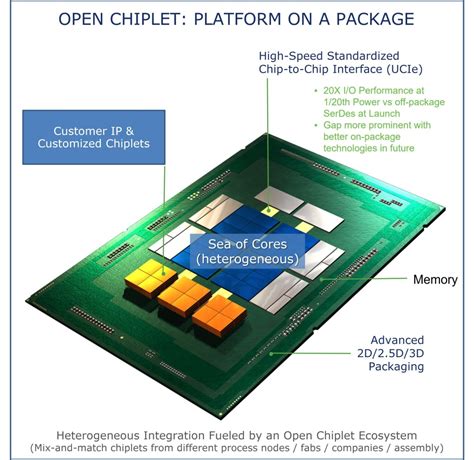

In the rapidly evolving world of semiconductor technology, chiplet standardization has become a pivotal topic. As we move towards a future where die-to-die interfaces play a crucial role in system integration, the need for a universal interface standard is more evident than ever. This article delves into the concept of chiplet standardization and explores the potential of universal die-to-die interfaces, going beyond the existing UCIe (Universal Chiplet Interface) standard.

**Understanding Chiplet Standardization**

Chiplets are smaller, specialized chips that can be combined to create larger, more complex systems. The idea behind chiplet standardization is to ensure compatibility and interoperability among these diverse components. By establishing a set of common standards, manufacturers can design and produce chiplets that can be easily integrated into various applications.

**The Importance of Die-to-Die Interfaces**

Die-to-die interfaces are the key enablers of chiplet integration. These interfaces facilitate the communication between different chiplets, allowing them to work together as a cohesive system. With the increasing complexity of modern semiconductor designs, efficient and reliable die-to-die interfaces are essential for achieving high-performance and energy-efficient systems.

**Beyond UCIe: The Need for a Universal Standard**

UCIe, or the Universal Chiplet Interface, is a promising standard that aims to simplify chiplet integration. However, as the industry continues to evolve, it becomes evident that a more versatile and comprehensive standard is needed.

**Challenges and Opportunities**

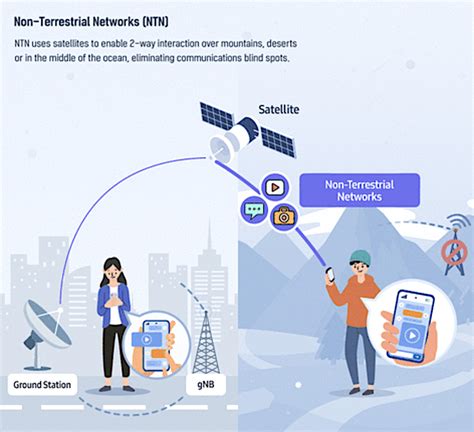

1. **Compatibility**: Ensuring compatibility between various chiplet types and applications remains a significant challenge. A universal standard should cater to a wide range of use cases while maintaining a high level of interoperability.

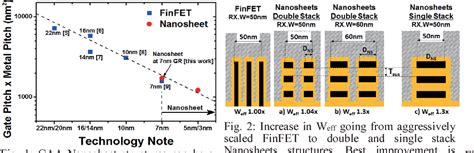

2. **Performance**: As system complexity increases, the demand for higher performance die-to-die interfaces also grows. The standard should support high-speed data transfer and low-latency communication.

3. **Energy Efficiency**: With the growing concern for environmental sustainability, energy-efficient interfaces are crucial. The standard should minimize power consumption while maintaining optimal performance.

4. **Scalability**: As the industry continues to scale, the standard should be adaptable to future advancements in technology and accommodate the integration of new chiplet types.

**Proposing a Universal Die-to-Die Interface Standard**

To address these challenges and capitalize on the opportunities, we propose a new universal die-to-die interface standard. This standard should:

1. **Embrace Existing Standards**: Build upon the strengths of existing standards, such as UCIe, while addressing their limitations.

2. **Support Various Interconnect Technologies**: Be adaptable to various interconnect technologies, such as through-silicon via (TSV) and wafer-level packaging (WLP).

3. **Foster Industry Collaboration**: Encourage collaboration among manufacturers, researchers, and other stakeholders to ensure a cohesive and comprehensive approach.

4. **Promote Innovation**: Encourage the development of new chiplet types and applications by providing a robust and versatile interface standard.

By adopting this universal die-to-die interface standard, the semiconductor industry can overcome the limitations of existing standards and accelerate the development of next-generation systems. With the right balance between compatibility, performance, energy efficiency, and scalability, this new standard has the potential to revolutionize chiplet integration and drive innovation in the semiconductor industry.